2.5 KiB

OI!STER

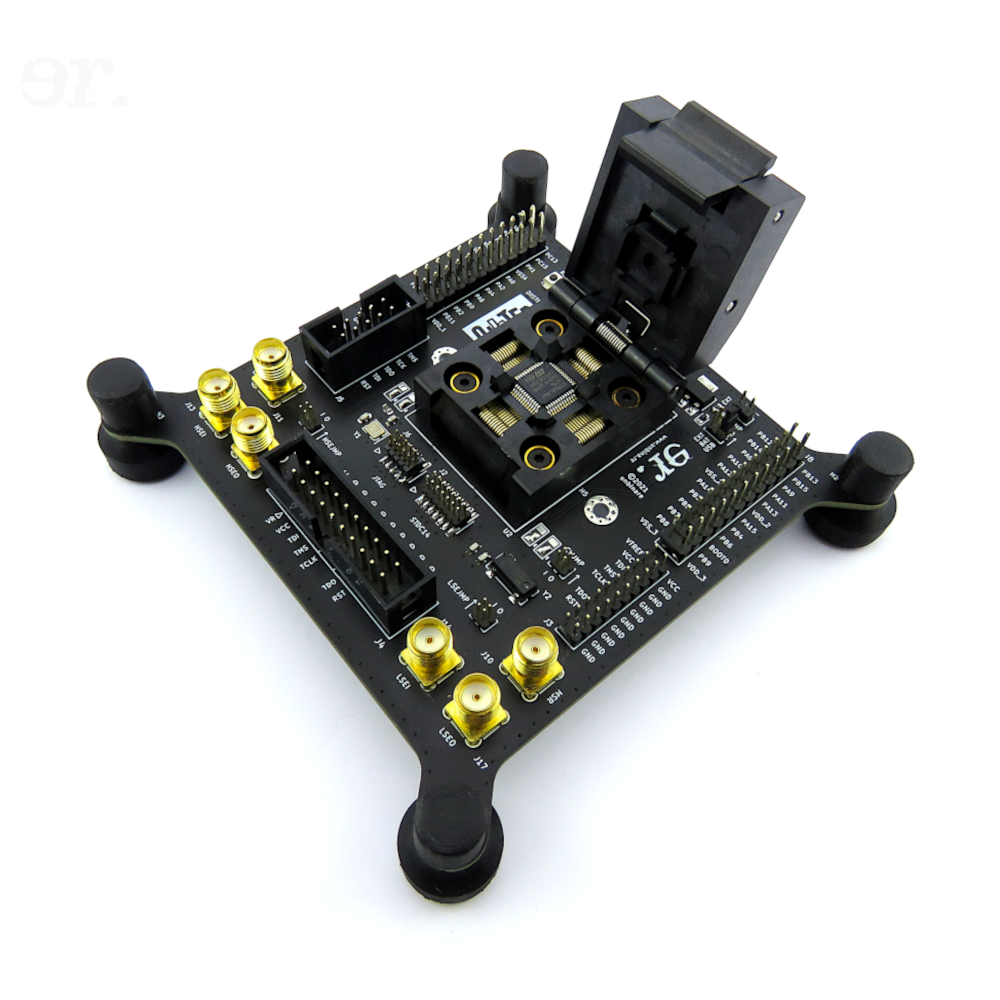

The OI!STER is a target board centered on salvaged STM32L5 microcontrollers (QFP48 package). It is engineered to support a wide range of hardware research activities, including advanced debugging, glitching, and fault-injection experiments. Power can be supplied via three interchangeable methods, enabling seamless transitions between laboratory benches and field deployments without any hardware modification. All 48 MCU pins are exposed through dual 24-pin headers on the board's upper edge, while additional debug, clock, and power-rail interfaces provide extensive configurability for custom test fixtures and side-channel analysis.

Features

Flexible power provisioning

- USB-C connector for bench-top power.

- Rear-mounted CR2032 coin cell for portable operation.

- External voltage input for field deployments.

Full MCU pin accessibility

- All 48 pins of the STM32L5 QFP48 MCU routed to two 24-pin headers on the upper edge, facilitating unobstructed connection of external instrumentation.

Debugging interfaces

- Five dedicated debug headers exposing standard SWD/JTAG signals.

- Compatibility with Open Source debugging tools such as HydraBus and Black Magic Probe.

SMA connector suite (three functional pairs)

- Pair 1: Connected to the low-speed external crystal (LSE) input.

- Pair 2: Connected to the high-speed external crystal (HSE) input.

- Pair 3: Connected to a configurable power-rail node for side-channel or fault injection.

- Each SMA port can be electrically isolated by lifting a miniature jumper, allowing rapid reconfiguration.

Configurable clock and power rails

- Solder jumpers on external clock traces and on each MCU power rail.

- Eliminates the need for PCB redesign when experimenting with alternative clock sources or power-distribution topologies.

Research-oriented design

- Combines comprehensive signal access with modular power options, making the board a versatile foundation for reverse engineering, sidechannel analysis and fault-injection investigations targeting the STM32L5 family.

Funding

This project received funding through NGI0 Entrust, a fund established by NLnet with financial support from the European Commission's Next Generation Internet program. Learn more at the NLnet project page.